# **CMX990**

# CML Microcircuits GMSK Packet Data Modem and RF Transceiver

D/990/1 April 2004 Advance Information

#### **Features**

- Single Chip RF Transceiver and GMSK Modem

- IF, RF, Control and Synthesizer Stages

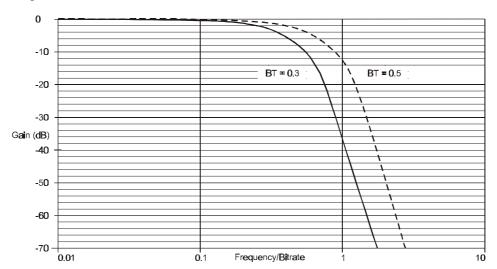

- Selectable B<sub>t</sub> = 0.3 or 0.5

- · Full Mobitex Compatibility

- Packet and Freeformat (Raw) Data

- Versatile Data Rates: 4kbps to 16kbps

- · Simple Parallel Interfacing

- · Low-Power, Low Profile, Low-Cost BOM

- Flexible System Clocks

# **Applications**

- · Narrowband Data Over Radio

- Mobitex Data Terminals

- 400MHz to 1GHz Radio Data Systems

- · Radio Modems

- Wireless Telemetry

- SCADA Terminals

- Suitable for EN 300 113 and FCC CFR 47 Part 90 Applications

# 1. Brief Description

A single-chip GMSK packet-data modem and RF transceiver, the CMX990 provides the majority of circuits and functions, including host  $\mu$ C interfaces, to implement a full-feature 'wireless modem' subsystem. The CMX990 can operate in RF ranges of 400MHz to 1GHz at data rates of 4 to 16 kbps and is fully Mobitex compatible.

With a minimum of external components and circuits, this half-duplex device provides on-chip: a flexible, formattable GMSK packet and freeformat modem, a dual operation synthesiser fed from an external source, IF and RF stages for both Rx and Tx modes, and auxiliary ADCs and DACs for system control and monitoring.

This versatile GMSK modem is programmable to both packet and freeformat data operations via an efficient task-oriented Rx and Tx format and command structure, which is combined with data scrambling, interleaving and FEC and CRC capabilities. Rx data acquisition, extraction and tracking abilities, allied with Rx data quality feedback, allow the CMX990 to operate seamlessly in varying signal environments.

IF and RF functions in the Tx path handle all the required signal mixing and up-conversion to produce the FM modulation for the final external PA circuitry. In the Rx path these circuits provide initial selectivity and rejection characteristics and mix down the inputs to provide baseband signals for the modem.

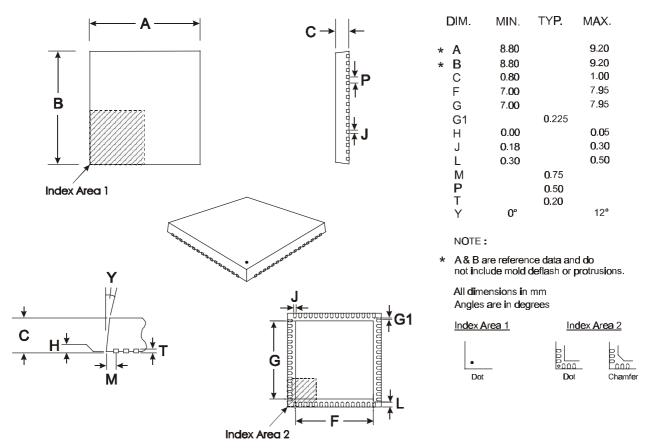

Comprehensive internal and external system control and monitoring is provided by the 8-bit host interface registers and the on-chip ADCs and DACs. Requiring a power supply input in the range 3.0 to 3.6 Volts, the CMX990 can be used in wireless products designed to comply with such standards as EN 300 113 and FCC CFR 47 Part 90. Operating over a temperature range of -40°C to +85°C, the CMX990 consolidates the core radio modem functions to enable a new generation of small, narrow-band wireless data modems. The CMX990 comes in a 64-pin low profile VQFN package.

#### **CONTENTS**

| <u>Section</u> |         |         | <u>P</u>                                       | age        |

|----------------|---------|---------|------------------------------------------------|------------|

| 1.             | Brief D | escript | tion                                           | .1         |

| 2.             | Block   | Diagran | n                                              | .4         |

| 3.             | Signal  | List    |                                                | .5         |

| 4.             | Extern  | al Com  | ponents                                        | .8         |

|                | 4.1     | Proces  | ssor Interface                                 | .9         |

|                | 4.2     | Synthe  | esiser and TCXO1                               | 0          |

|                | 4.3     | Transi  | mit1                                           | 1          |

|                | 4.4     | Receiv  | ve1                                            | 2          |

|                | 4.5     | Power   | Supply Decoupling and Layout1                  | 3          |

| 5              | Genera  | al Desc | ription1                                       | 5          |

|                | 5.1     | Baseb   | and Modem1                                     | 5          |

|                |         | 5.1.1   | Description of Blocks1                         | 5          |

|                |         | 5.1.2   | Modem - μC Interaction1                        | 7          |

|                |         | 5.1.3   | Data Formats1                                  | 8          |

|                |         | 5.1.4   | Programmer's View of the Modem2                | 20         |

|                |         | 5.1.5   | CRC, FEC, Interleaving and Scrambling Details3 | 37         |

|                |         | 5.1.6   | Application Notes4                             | Ю          |

|                | 5.2     | μC Inte | erface4                                        | 14         |

|                |         | 5.2.1   | Memory Map and Interface4                      | 14         |

|                |         | 5.2.2   | Power-on and Reset4                            | 15         |

|                |         | 5.2.3   | Clock Control4                                 | 16         |

|                |         | 5.2.4   | Status Registers4                              | 17         |

|                |         | 5.2.5   | Write Only Registers4                          | 18         |

|                |         | 5.2.6   | Read Only Registers5                           | 52         |

|                | 5.3     | Auxilia | ary DAC and ADC5                               | 54         |

|                | 5.4     | Synthe  | esiser5                                        | 57         |

|                | 5.5     | RF and  | d IF5                                          | 59         |

|                |         | 5.5.1   | Receiver Section5                              | 59         |

|                |         | 5.5.2   | Transmitter Section6                           | 30         |

|                |         | 5.5.3   | Alternative Receiver Architecture6             | <b>60</b>  |

| 6.             | Applic  | ation N | otes6                                          | 62         |

|                | 6.1     | Gener   | al6                                            | <b>52</b>  |

|                | 6.2     | Transı  | mitter6                                        | <b>52</b>  |

|                | 6.3     | Receiv  | ver6                                           | <b>3</b> 4 |

|                | 6.4     | Variab  | ole Bt6                                        | <b>39</b>  |

| 7.             | Perfori | mance   | Specification7                                 | <b>7</b> 1 |

|                | 7.1     |         | ical Performance7                              |            |

|                | 7.2     | Packa   | ging7                                          | 77         |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

**Note:** This product is in development: Changes and additions will be made to this specification. Items marked TBD or left blank will be included in later issues.

Information in this data sheet should not be relied upon for final product design.

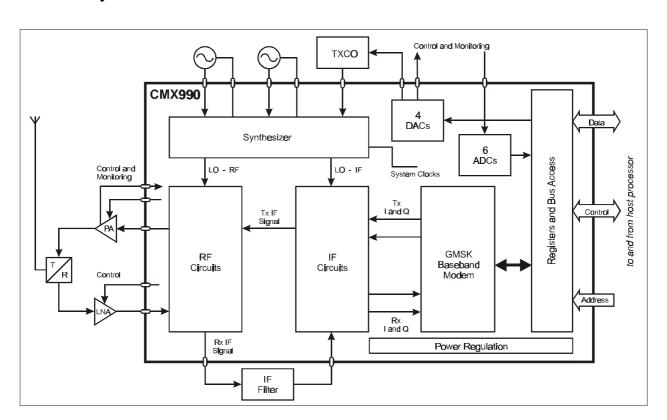

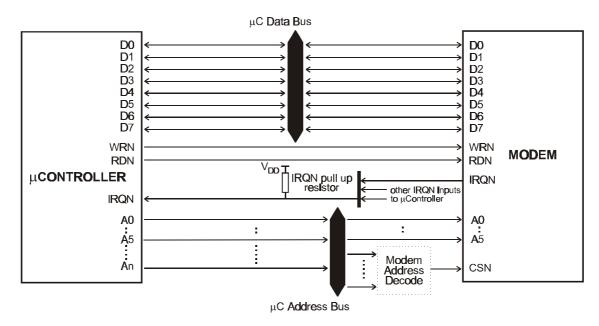

# 2. Block Diagram

Figure 1 Block Diagram

# 3. Signal List

| Package Signal |           | I    | Description                                                          |  |

|----------------|-----------|------|----------------------------------------------------------------------|--|

| Pin No.        | Name      | Type |                                                                      |  |

| 1              | PA-CNTL   | O/P  | DAC0 output to control PA power.                                     |  |

| 2              | TX FB     | I/P  | Tx feedback input signal.                                            |  |

| 3              | TXIF2     | ВІ   | Offset loop filter connection.                                       |  |

| 5              | TXIF1     | ВІ   | Offset loop filter connection.                                       |  |

| 7              | TXPLL     | O/P  | Tx Phase Detector output.                                            |  |

| 8              | RF IN A   | I/P  | RF input A for received signal.                                      |  |

| 9              | RF IN B   | I/P  | RF input B for received signal.                                      |  |

| 11             | IF OUT    | O/P  | Output to the external IF filter.                                    |  |

| 14             | LNA ON    | O/P  | Digital output to turn on external LNA block.                        |  |

| 16             | IF IN     | I/P  | Input from the external IF filter.                                   |  |

| 43             | DAC3      | O/P  | Spare D/A output.                                                    |  |

| 44             | DAC2      | O/P  | Spare D/A output.                                                    |  |

| 45             | ADC5      | I/P  | Spare A/D input.                                                     |  |

| 46             | ADC4      | I/P  | Spare A/D input.                                                     |  |

| 47             | OP2T      | O/P  | Uncommitted op-amp 2 output, internally connected to ADC3.           |  |

| 48             | OP2N      | I/P  | Uncommitted op-amp 2 negative input.                                 |  |

| 49             | OP2P      | I/P  | Uncommitted op-amp 2 positive input.                                 |  |

| 50             | OP1T      | O/P  | Uncommitted op-amp 1 output, internally connected to ADC2.           |  |

| 51             | OP1N      | I/P  | Uncommitted op-amp 1 negative input.                                 |  |

| 52             | OP1P      | I/P  | Uncommitted op-amp 1 positive input.                                 |  |

| 53             | REFCLK    | I/P  | Master clock input from external TCXO.                               |  |

| 54             | TCXO-CNTL | O/P  | DAC1 output to control TCXO.                                         |  |

| 55             | TCXO-TEMP | I/P  | A/D input to measure TCXO temperature, internally connected to ADC1. |  |

| 56             | LOCLKN    | I/P  | Inverted input from the RF Oscillator circuit.                       |  |

| 57             | LOCLK     | I/P  | Input from the RF Oscillator circuit.                                |  |

| 59             | MAINPLL   | O/P  | Main PLL output, connect to external filter.                         |  |

| 61             | AUXPLL    | O/P  | Aux PLL output, connect to external filter.                          |  |

| 63             | IFCLK     | I/P  | Input from the IF Oscillator circuit.                                |  |

| 64             | PA-TEMP   | I/P  | A/D input to measure PA temperature, internally connected to ADC0.   |  |

| Package<br>Q1 | Signa | I    | Description                                                                                                                                                                                                           |  |

|---------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.       | Name  | Type |                                                                                                                                                                                                                       |  |

| 17            | A5    | I/P  | Register address select logic inputs.                                                                                                                                                                                 |  |

| 18            | A4    | I/P  | "                                                                                                                                                                                                                     |  |

| 19            | А3    | I/P  | "                                                                                                                                                                                                                     |  |

| 20            | A2    | I/P  | "                                                                                                                                                                                                                     |  |

| 21            | A1    | I/P  | "                                                                                                                                                                                                                     |  |

| 22            | A0    | I/P  | "                                                                                                                                                                                                                     |  |

| 29            | RDN   | I/P  | Read. An active low logic level input used to control the reading of data from the modem into the controlling $\mu C$ .                                                                                               |  |

| 30            | WRN   | I/P  | Write. An active low logic level input used to control the writing of data into the modem from the controlling µC.                                                                                                    |  |

| 31            | CSN   | I/P  | Chip Select. An active low logic level input used to enable a data read or write operation.                                                                                                                           |  |

| 32            | IRQN  | O/P  | A 'wire-ORable' output for connection to the host Interrupt Request input. This output has a low impedance pull down to Vss when active and is high impedance when inactive. An external pullup resistor is required. |  |

| 34            | D7    | ВІ   | Tri-state μC interface data line.                                                                                                                                                                                     |  |

| 35            | D6    | ВІ   | п                                                                                                                                                                                                                     |  |

| 36            | D5    | ВІ   | п                                                                                                                                                                                                                     |  |

| 37            | D4    | ВІ   | "                                                                                                                                                                                                                     |  |

| 38            | D3    | ВІ   | "                                                                                                                                                                                                                     |  |

| 39            | D2    | ВІ   | "                                                                                                                                                                                                                     |  |

| 40            | D1    | ВІ   | п                                                                                                                                                                                                                     |  |

| 41            | D0    | BI   | "                                                                                                                                                                                                                     |  |

| Package<br>Q1 | Signal                |       | Description                                                         |

|---------------|-----------------------|-------|---------------------------------------------------------------------|

| Pin No.       | Name                  | Туре  |                                                                     |

| 4             | $V_{DD} Tx$           | Power | Power supply to Tx IF and RF circuits.                              |

| 6             | $V_{SS} Tx$           | Power | Return for V <sub>DD</sub> Tx, good decoupling required.            |

| 10            | $V_{DD} Rx1$          | Power | Power supply to Rx RF circuits.                                     |

| 12            | V <sub>SS</sub> Rx1   | Power | Return for V <sub>DD</sub> Rx1, good decoupling required.           |

| 13            | $V_{SS}$ Rx2          | Power | Return for V <sub>DD</sub> Rx2, good decoupling required.           |

| 15            | $V_{DD} Rx2$          | Power | Power supply to Rx IF circuits.                                     |

| 23            | $V_{DD}$ Dig          | Power | Power supply to base band digital circuits.                         |

| 24            | $V_{\text{DD}}$ Ana   | Power | Power supply to aux ADC, DAC, OP1/2 circuits.                       |

| 25            | $V_{BIAS}$            | O/P   | Output of internal bias generator, decouple to $V_{\text{SS}}$ Ana. |

| 26            | $V_{\text{SS}}$ Ana   | Power | Return for V <sub>DD</sub> Ana, good decoupling required.           |

| 27            | $V_{SS}$ Dig          | Power | Return for V <sub>DD</sub> Dig, good decoupling required.           |

| 28            | $V_{SS}H$             | Power | Return for V <sub>DD</sub> H, good decoupling required.             |

| 33            | $V_{DD}$ H            | Power | Power supply to host interface and 2.5V regulator circuit.          |

| 42            | V-CONT                | O/P   | Control signal for external regulating transistor.                  |

| 58            | V <sub>SS</sub> Synth | Power | Return for V <sub>DD</sub> Synth, good decoupling required.         |

| 60            | V <sub>DD</sub> VCO   | Power | Power supply to the VCO charge pump, decouple to $V_{\rm SS}$ H.    |

| 62            | V <sub>DD</sub> Synth | Power | Power supply to synthesiser circuits.                               |

Notes: I/P = Input

O/P = Output

BI = Bidirectional

T/S = 3-state Output

NC = No Connection

# 4. External Components

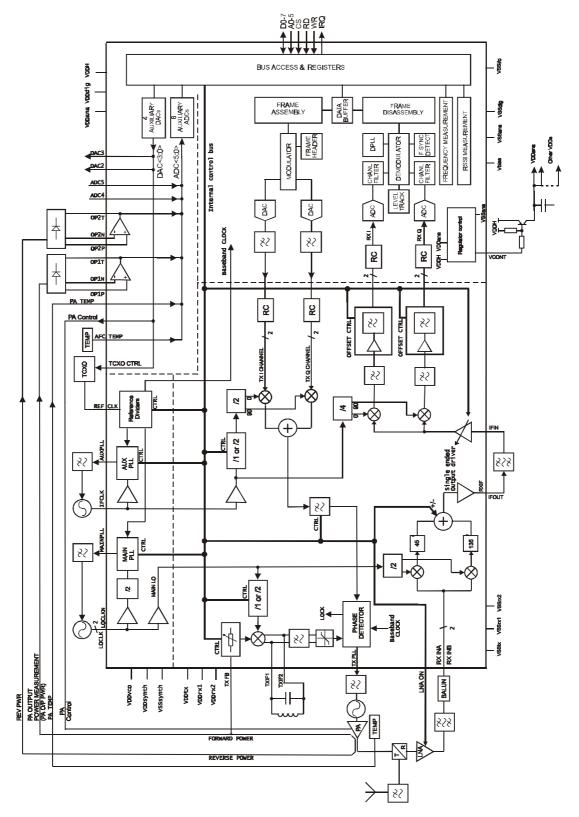

Figure 2 CMX990 Pin Overview

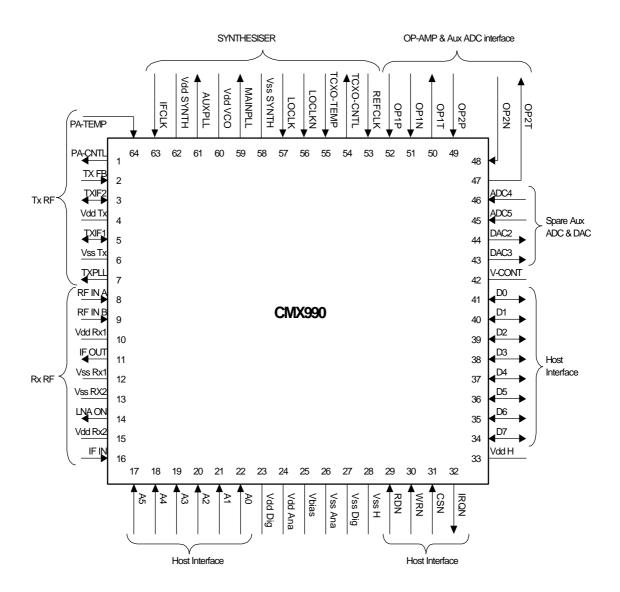

# 4.1 Processor Interface

Figure 3 Recommended External Configuration - Processor Interface

# 4.2 Synthesiser and TCXO

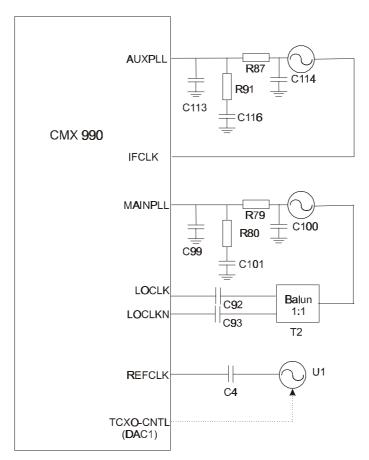

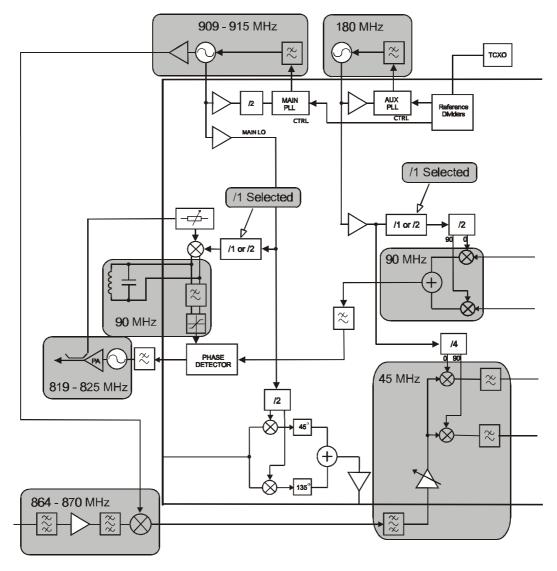

The CMX990 synthesiser section provides two independent synthesisers. The PLLs implement a Type II loop with a phase / frequency phase detector providing an output of a charge pump current. Various types of loop filter can be used and should be optimised for VCO gain of a particular design. Figure 4 gives typical configuration and values.

Figure 4 Recommended External Components - Synthesiser and TCXO

| C4   | 1 nF   | C114 | 1 nF                   |

|------|--------|------|------------------------|

| C92  | 1 nF   | C116 | 150 nF                 |

| C93  | 1 nF   | T2   | TCM4-25                |

| C99  | 27 nF  | R79  | $2.7~\mathrm{k}\Omega$ |

| C100 | 27 nF  | R80  | $1.2~\mathrm{k}\Omega$ |

| C101 | 680 nF | R87  | $39~\mathrm{k}\Omega$  |

| C113 | 1 nF   | R91  | $1.5~\mathrm{k}\Omega$ |

|      |        | U1   | See notes              |

#### Notes:

- 1 Resistors ±2%, capacitors ±5% unless otherwise stated.

- 2 For optimum lock time / phase noise it is recommended C113 and C116 use a low piezo type such as PPS film; optimum performance is not guaranteed with X7R or Y5V types.

- 3 U1 Should be a VCTCXO or TCXO depending on application requirements. A typical device is the Golledge GTXO-81. The CMX990 has a high impedance input suitable for use with oscillators with clipped sine wave output. An external DC blocking capacitor (as shown, C4) is required.

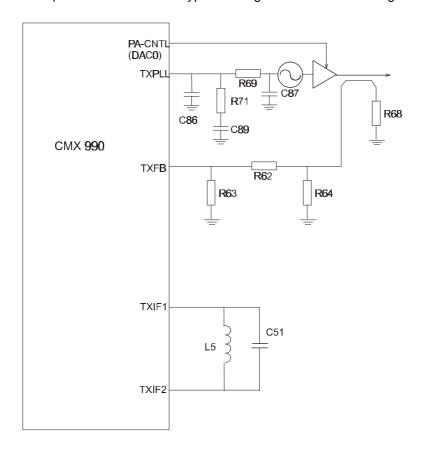

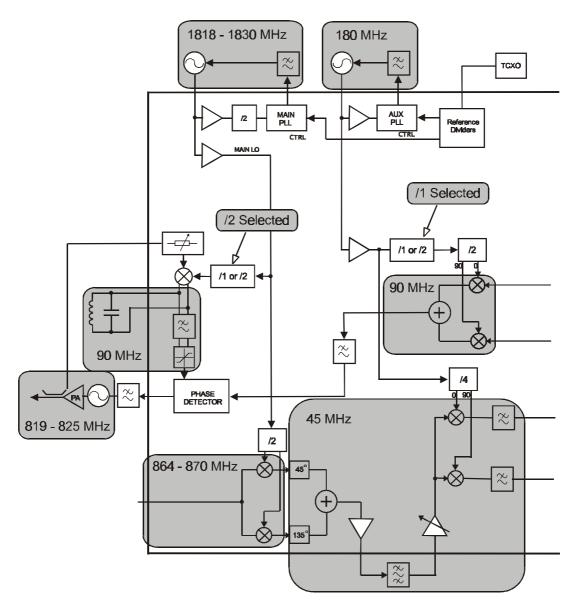

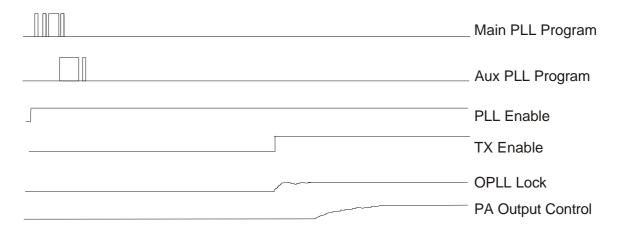

#### 4.3 Transmit

The CMX990 transmitter uses an offset phase-locked loop to accurately modulate RF signals. Details are contained in subsequent sections of this document. The components used around the CMX990 will depend on application requirements however a typical configuration is shown in Figure 5.

Figure 5 Recommended External Components - Transmit

| C51 | 6.8 pF | R62 | $18 \Omega$  |

|-----|--------|-----|--------------|

| C86 | 15 nF  | R63 | $270 \Omega$ |

| C87 | TBD nF | R64 | $270 \Omega$ |

| C89 | 68 nF  | R68 | $47 \Omega$  |

|     |        | R69 | $10~\Omega$  |

| L5  | 270 nH | R71 | $36 \Omega$  |

#### Notes:

- 1 Resistors  $\pm 2\%$ , capacitors  $\pm 5\%$  unless otherwise stated.

- 2 The coupler may be a packaged type (e.g. 0869CP14A090) or printed on the PCB; alternatively a sample of the output can be obtained with a resistive or capacitive tap.

- 3 Tx loop filter components need to be optimised for selected VCO.

- Components between TXIF1 and TXIF2 act as a resonant load to the mixer. They should be matched to the selected IF frequency whilst attenuating its odd harmonics. The Q of this filter can be controlled by changing the ratio of C51 to L5 whilst the centre frequency can be maintained by keeping the product of C51 and L5 a constant. A higher value of C51 will give a higher Q. The Q should not be so high as to prevent accommodation of the natural frequency range of the VCO. The values shown are approximate for an IF of 90MHz. Approximate values for an IF of 45MHz are 18pF and 560nH.

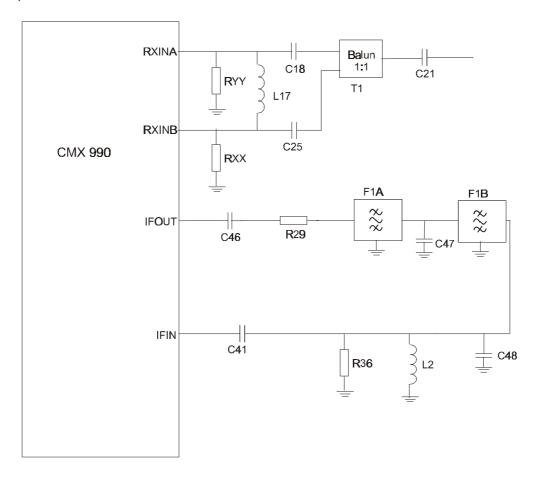

#### 4.4 Receive

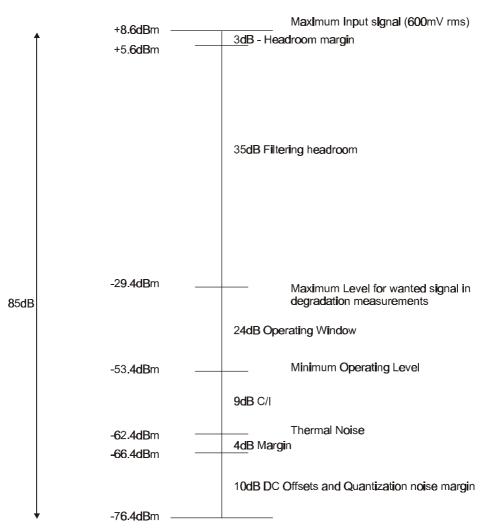

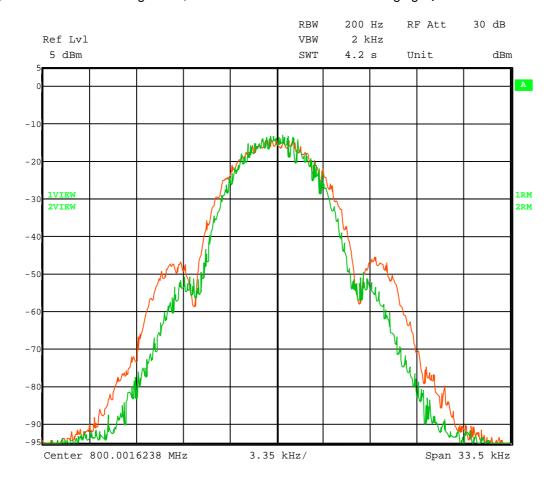

The receiver relies on external LNA, filtering and T/R switch; details can be found in the following sections. The 1<sup>st</sup> mixer in the CMX990 has a differential input. To ensure optimum performance a balun is required when driving from typical LNAs or filters. The balun may be a transformer type, which is implemented using LC networks. Suitable matching components around the balun, selected for the desired operating frequency, provide matching to  $50\Omega$ . Figure 6 shows a typical configuration for 800 - 840 MHz operation.

Figure 6 Recommended External Components - Receive

| C18 | 5 pF   | L2  | 1.2 μΗ                 |

|-----|--------|-----|------------------------|

| C21 |        | L17 | 15 nH                  |

| C25 | 5 pF   | T1  | $2.7~\mathrm{k}\Omega$ |

| C41 | 1 nF   | R29 | $330 \Omega$           |

| C46 | 10 nF  | R36 | $39~\mathrm{k}\Omega$  |

| C47 | 15 pF  | RXX | $100 \Omega$           |

| C48 | 5.6 pF | RYY | $100~\Omega$           |

|     | •      | F1  | 45G7B1                 |

#### Notes:

- 1 Resistors  $\pm 2\%$ , capacitors  $\pm 5\%$  unless otherwise stated.

- 2 F1 is a 4 pole crystal filter with a ±3.5kHz pass-band, implemented as a matched pair. The recommended part is from Golledge, however other parts may be equally suitable although matching arrangements will vary. When selecting and matching a crystal filter care should be taken to ensure a flat pass-band.

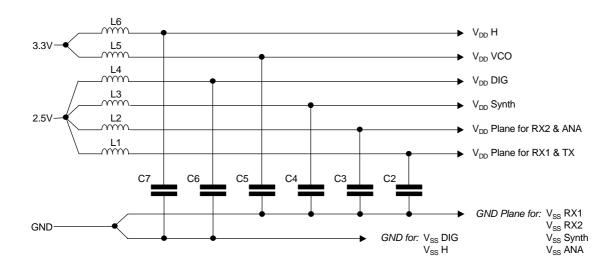

# 4.5 Power Supply Decoupling and Layout

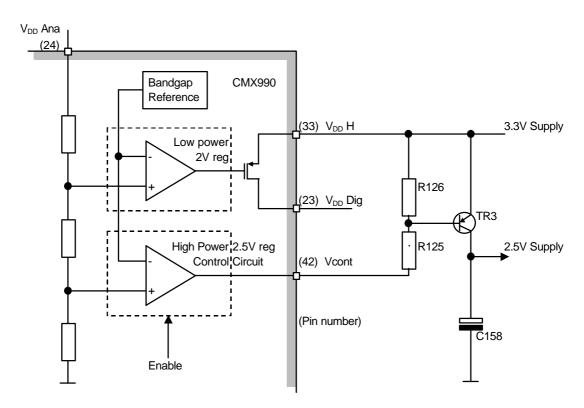

The CMX990 has dual supply voltages: a 3.3V supply is required for the PLLs and charge pump circuits and for the digital I/O pads, and a 2.5V supply (with separate decoupling) is required for the RF sections (Rx1, Rx2, Tx) as well as the baseband analogue and digital circuits.

The 3.3V supply must be provided by an external regulator circuit. The 2.5V supply may be provided by an external regulator, or alternatively may be derived from the 3.3V supply using an off-chip low dropout transistor in conjunction with the on-chip control circuit (enabled by register PowerUp1 bit 5) - an example of this arrangement is shown in Figure 7. Whichever method is used to generate the 2.5V supply, the 2.5V regulator may be turned off while the CMX990 is quiescent in order to save power. The CMX990 will then allow the supply to drop to 2.0V, at which point it will be clamped by a separate on-chip micropower regulator. This is done so that the data in the on-chip registers and memories is not lost. The main 2.5V regulator circuit must be powered up again and allowed to settle before any RF or analogue circuitry, or the clock to the internal logic, is enabled. In other words, PowerUp1 (bits 7-6 and 4-0) and PowerUp2 (bits 7-4 and 0) must not be set high until the main 2.5V supply has been reestablished.

The circuit shown in Figure 7 is an example, and will require that the 3.3V supply is regulated to within +/-5%. This is necessary to ensure that the PNP transistor shown (TR3) does not enter saturation, taking worst case ambient conditions and bandgap / component tolerances into account.

Figure 7 Voltage Regulator Connections

C158 100 μF R125 330  $\Omega$ TR3 PMBT4403 R126 47 k $\Omega$

Resistors ±5%, capacitors and inductors ±20% unless otherwise stated.

© 2004 CML Microsystems Plc 13 D/990/1

Figure 8 Power Supply Connections and De-coupling

| C2 | 10 nF | L1 | TBA |

|----|-------|----|-----|

| C3 | 10 nF | L2 | TBA |

| C4 | 10 nF | L3 | TBA |

| C5 | 10 nF | L4 | TBA |

| C6 | 10 nF | L5 | TBA |

| C7 | 10 nF | L6 | TBA |

Resistors ±5%, capacitors and inductors ±20% unless otherwise stated.

# **Layout Recommendations**

To achieve good noise performance, decoupling of  $V_{\text{BIAS}}$  and all supplies is very important as is protection of the receive path from extraneous in-band signals. It is recommended that the printed circuit board is laid out with a ground plane in the CMX990 area to provide a low impedance connection between the  $V_{\text{SS}}$  pins and all  $V_{\text{DD}}$  and  $V_{\text{BIAS}}$  decoupling capacitors. As shown in Figure 8 the ground for  $V_{\text{SS}}$  digital signals should be kept separate from that used for analogue / RF signals. The digital ground should be routed back to a suitable star point.

The CMX990 package has a copper area connected to ground under the main body of the IC. This pad should be connected to analogue ground. It will be noted that caution should be exercised over placing any tracks underneath the CMX990. Further any vias other than ground should be avoided under the device unless manufacturers can guarantee that the exposed ground pad on the CMX990 will not cause shorts while a good electrical contact is maintained between the device and ground.

Apart from these recommendations normal RF layout practices should apply such as keeping tracks as short as possible, equal track lengths on differential inputs, care with coupling between tracks etc.

# 5. General Description

The CMX990 comprises a baseband modem and an associated RF section to provide the air-interface to the required Mobitex standard. Device control and status is transferred via a set of memory mapped registers. The following paragraphs provide a description of operation of each of the sections that make up the device.

The CMX990 is composed of 5 main sections:

- 5.1 Baseband modem

- 5.2 uC interface

- 5.3 Auxiliary ADC and DAC

- 5.4 Synthesiser

- 5.5 RF and IF

Each of the above will be described in its own section below:

#### 5.1 Baseband Modem

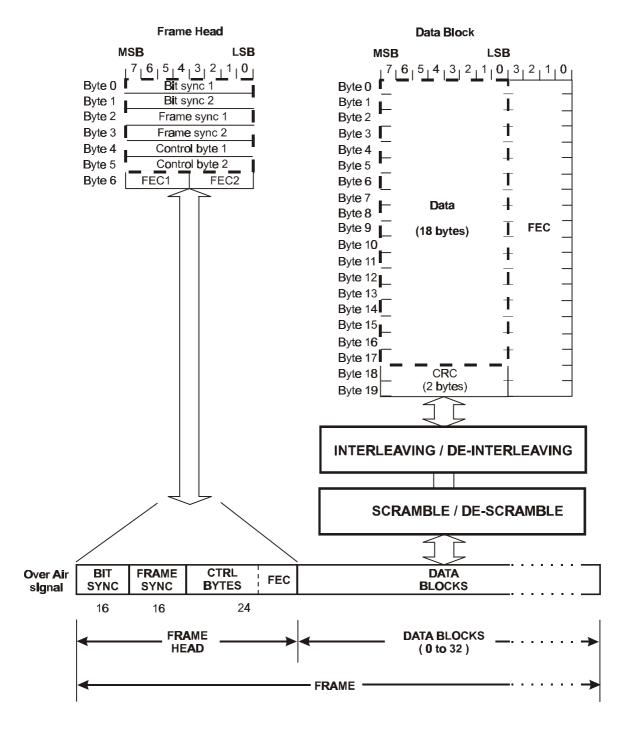

This section has been designed to be compliant with the appropriate sections of the "Mobitex Interface Specification" including Short Block Frame formatting for the extended battery saving protocol. References to 'data blocks' in this section apply to both the normal (18 byte) Data Block and the smaller (4 byte) Short Data Block.

The function of this section is further divided into Receive and Transmit sections that operate in half duplex.

In transmit mode the data is encoded according to the Mobitex standard. This includes the calculation and appending of a Cyclic Redundancy Checksum (CRC) and Forward Error Correction (FEC), and Interleaving to reduce the effects of noise. The subsequent NRZ data stream is then filtered digitally and the resulting digital data processed to produce an I and Q signal as the baseband form of the required FM signal. These are converted to analogue signals via D-A converters and passed to the RF section for subsequent transmission.

In receive mode, the analogue I and Q representations, at baseband, of the FM signal from the RF section are converted to digital signals via A-D converters. These signals are digitally filtered to suppress the adjacent channels and demodulated digitally. The resulting signal is then filtered, to optimise the signal to noise performance, before slicing to resolve into a digital bit stream. Mobitex specified error correction and de-interleaving is applied and the resulting data is presented for transfer to an external processor.

#### 5.1.1 Description of Blocks

#### Status and Data Quality Registers

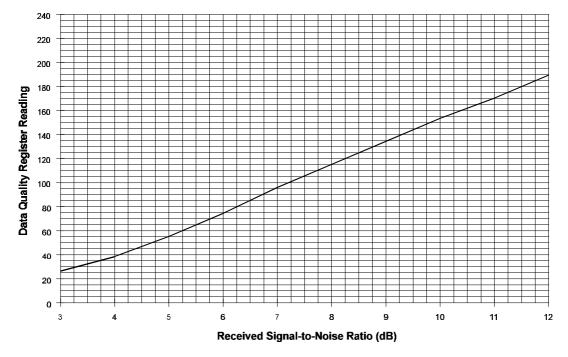

8-bit registers which the  $\mu C$  can read to determine the status of the modem and the received data quality.

# **Command, Mode and Control Registers**

The values written by the µC to these 8-bit registers control the operation of the modem.

#### **Data Buffer**

An 18-byte buffer used to hold receive or transmit data to or from the  $\mu$ C.

#### Frame Assembly / Disassembly

Each of these blocks consists of 4 circuits which generate (in transmit mode) or check (in receive mode) the bits of both short and normal Mobitex data blocks.

#### CRC Generator/Checker

A circuit which generates (in transmit) or checks (in receive) the CRC bits, which are included in transmitted Mobitex data blocks so that the receive modem can detect transmission errors.

#### FEC Generator/Checker

In transmit mode this circuit calculates and adds the FEC (4 bits) to each byte presented to it. In receive mode the FEC information is used to correct most transmission errors that have occurred in Mobitex data blocks or in the Frame Head control bytes.

#### Interleave/De-interleave Buffer

This circuit interleaves data bits within a data block before transmission and de-interleaves the received data block so that the FEC system is best able to handle short noise bursts or signal fades.

#### Scramble/De-scramble

This block may be optionally used to scramble/de-scramble the transmitted and received data blocks. It does this by modulating the data with a 511-bit pseudorandom sequence, as described in section 5.1.5.4. Scrambling improves the transmitted spectrum, especially when repetitive sequences are to be transmitted.

#### **Frame Sync Detect**

This circuit, which is only active in receive mode, is used to look for the user specified 16-bit Frame Synchronisation pattern which is transmitted to mark the start of every frame.

#### Tx Modulator and Low Pass Filter

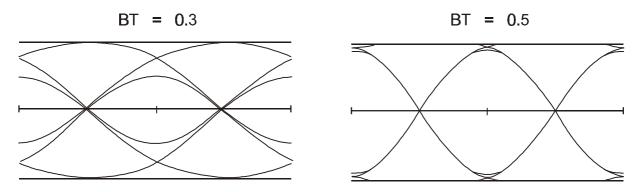

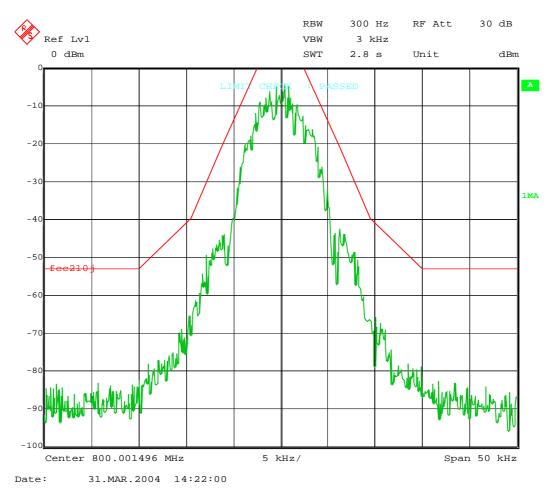

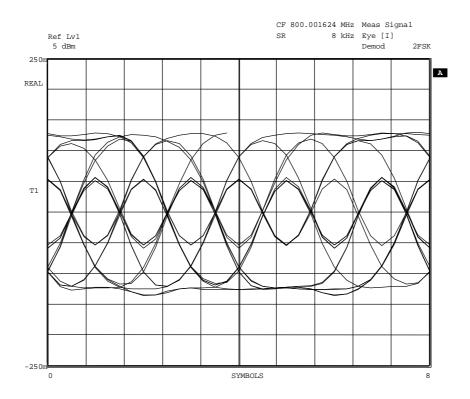

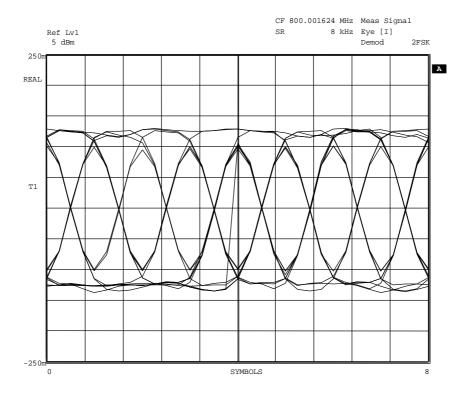

The filter is used in transmit mode and is a low pass transitional Gaussian filter having a 3dB loss at 0.3 or 0.5 times the bit rate (BT=0.3 or 0.5). See figure 9. This filter eliminates the high frequency components which would otherwise cause interference into adjacent radio channels.

The unmodulated baseband 'eye' diagrams of the transmitted signal is shown in Figure 10.

The Tx Modulator converts the baseband signal into an I and Q form which is passed to the Tx IF stage.

Figure 9 Typical Tx Baseband Filter Response

Figure 10 Baseband Transmitter Signal Eye Diagrams

#### **Rx Low Pass Filter**

This filter is a low pass transitional Gaussian filter having a 3dB loss at 0.56 times the bit rate (BT=0.56). It is used to reject HF noise to improve the BER.

#### **Level Track and DPLL**

These circuits, which operate only in receive mode, extract a bit rate clock from the received signal and measure the received signal amplitude and dc offset. This information is then used to extract the received bits and also to provide an input to the received Data Quality measuring circuit.

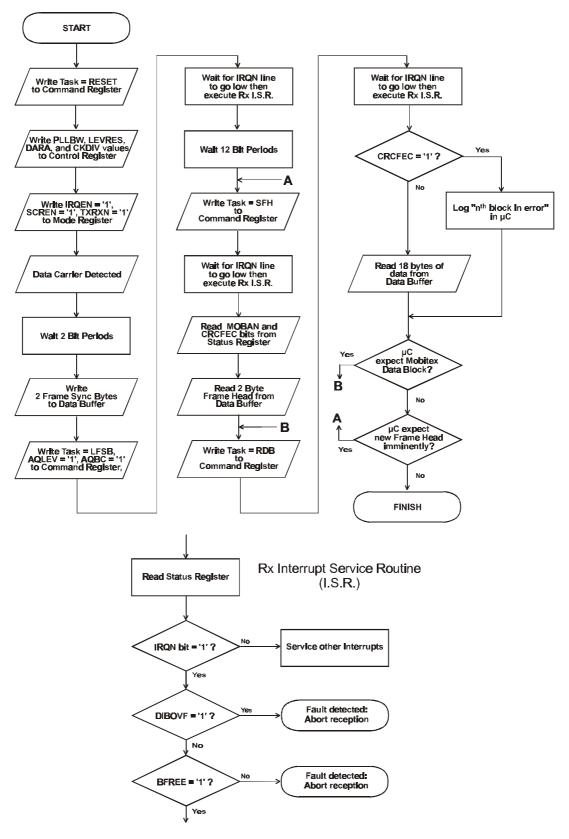

#### 5.1.2 Modem - μC Interaction

In general, data is transmitted over air in the form of messages, or 'Frames', consisting of a 'Frame Head' optionally followed by one or more formatted data blocks. The Frame Head includes a Frame Synchronisation pattern designed to allow the receiving modem to identify the start of a frame. The following data blocks are constructed from the 'raw' data using a combination of CRC (Cyclic Redundancy Checksum) generation, Forward Error Correction coding, Interleaving and Scrambling. Details of the message formats handled by this modem are given in section 5.3.

To reduce the processing load on the host  $\mu C$ , this modem has been designed to perform as much as possible of the computationally intensive work involved in Frame formatting and deformatting and (when in receive mode) in searching for and synchronising onto the Frame Head. In normal operation the modem will only require servicing by the  $\mu C$  once per received or transmitted data block.

Thus, to transmit a block, the host  $\mu C$  has only to load the unformatted (raw) binary data into the modem's data buffer then instruct the modem to format and transmit that data. The modem will then calculate and add the CRC bits as required, encode the result with Forward Error Correction coding, interleave then scramble the bits before transmission.

In receive mode, the modem can be instructed to assemble a block's worth of received bits, de-scramble and de-interleave the bits, check and correct them (using the FEC coding) and check the resulting CRC before placing the received binary data into the Data Buffer for the  $\mu C$  to read.

The modem can also handle the transmission and reception of unformatted data, to allow the transmission of special Bit and Frame Synchronisation sequences or test patterns.

#### 5.1.3 Data Formats

#### Raw data

If required the user may transmit and receive raw data. This is transferred between the host and device a byte (8 bits) at a time.

Note that it is important to have established frame synchronisation before receiving data to enable the receiving device to decode synchronously. The user may add error detection and correction by way of algorithms performed on the host device.

#### **General Purpose Formats**

In a proprietary system the user may employ the data elements provided by this device to construct a custom, over-air data structure.

For example, 16 bits of bit sync + 2 bytes of frame sync + 4 bytes of receiver and sender address + n data blocks would be sent as:

TQB (bit and frame sync) + TQB (addresses) + (n x TDB) + TSB

And received as:

$SFS + RSB + RSB + RSB + RSB + (n \times RDB)$

#### **Mobitex Frame Structure**

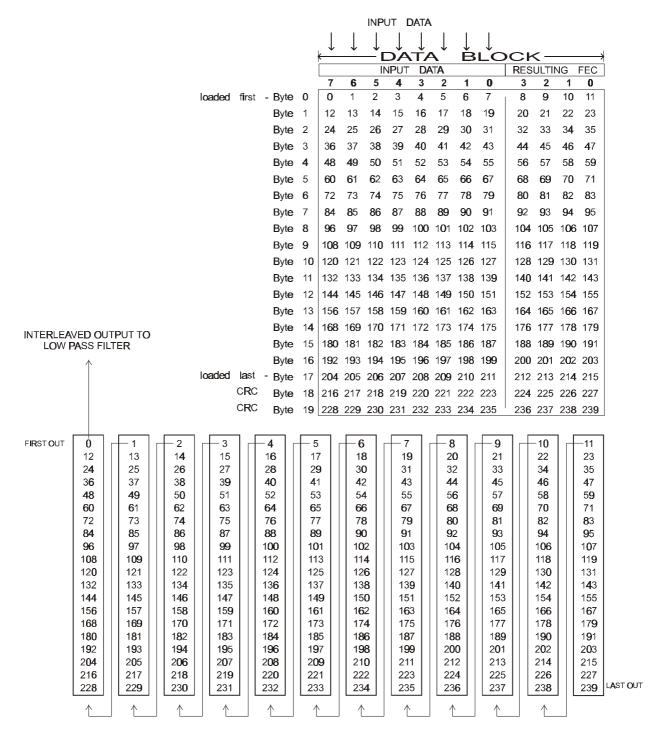

The Mobitex format for transmitted data is in the form of a Frame Head immediately followed by either 1 Short Data Block or a number of Data Blocks (0 to 32).

The Frame Head consists of 7 bytes:

2 bytes of bit sync:

1100110011001100 from base, 0011001100110011 from mobile bits are transmitted from left to right

2 bytes of frame sync:

System specific.

2 bytes of control data.

1 byte of FEC code, 4 bits for each of the control bytes:

bits 7-4 (leftmost) operate on the first control byte. bits 3-0 (rightmost) operate on the second control byte.

Each byte in the Frame Head is transmitted bit 7 (MSB) first to bit 0 (LSB) last.

The normal and short data blocks consist of:

18 bytes of data (Data Block) OR 4 bytes of data (Short Data Block).

2 bytes of CRC calculated from the data bytes.

4 bits of FEC code for each of the data and CRC bytes

The resulting data block bits are interleaved and scrambled before transmission.

Figure 11 shows how the over air signal is built up from Frame Sync and Bit Sync patterns, Control bytes and Data Blocks.

The binary data transferred between the modem and the host  $\mu C$  is that shown enclosed by the thick dashed rectangles near the top of the diagram.

Figure 11 Mobitex Over Air Signal Format

#### 5.1.4 Programmer's View of the Modem

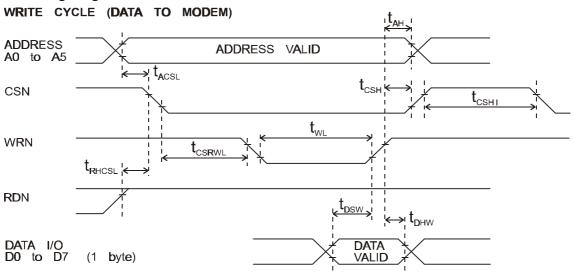

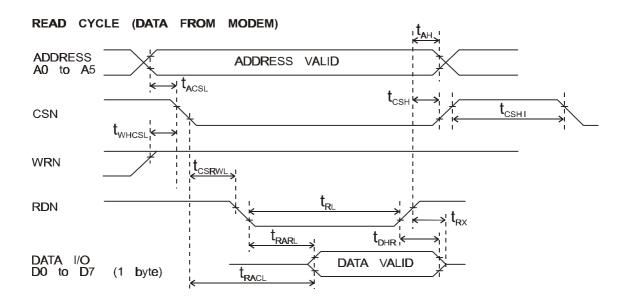

The modem appears to the programmer as a series of 8-bit read and write registers, individual registers being selected by the A0 to A5 address pins. Most of the baseband control for formatting or decoding the data is controlled by the following registers:

| Address | Write to Modem               | Read from Modem       |

|---------|------------------------------|-----------------------|

| \$00    | \$00 Data Buffer Data Buffer |                       |

| \$01    | Command Register             | Status 1 Register     |

| \$02    | Control Register             | Data Quality Register |

| \$03    | Mode Register                | Status 2 Register     |

#### 5.1.4.1 Data Buffer

This is an 18-byte read/write buffer which is used to transfer data (as opposed to command, status, mode, data quality and control information) between the modem and the host µC.

It appears to the  $\mu$ C as a single 8-bit register; the modem ensuring that sequential  $\mu$ C reads or writes to the buffer are routed to the correct locations within the buffer.

The  $\mu$ C should only access this buffer 2  $\mu$ s after the Status Register BFREE (Buffer Free) bit is set to '1'.

The buffer should only be written to while in Tx mode and read from while in Rx mode (except when loading Frame Sync detection bytes while in Rx mode).

#### 5.1.4.2 Command Register

Writing to this register tells the modem to perform a specific action or actions, depending on the setting of the TASK and acquire bits. The enable packet detect bit is used to indicate the presence of data signals in the receive path.

| Command Register \$01 |                      |                       | Write          |               |              |   |   |   |

|-----------------------|----------------------|-----------------------|----------------|---------------|--------------|---|---|---|

| Bit:                  | 7                    | 6                     | 5              | 4             | 3            | 2 | 1 | 0 |

|                       | Acquire<br>Bit Clock | Acquire<br>I Q Offset | Acquire<br>AFC | Enable packet | Task Control |   |   |   |

When it has no action to perform (but is not 'powersaved'), the modem will be in an 'idle' state. If the modem is in transmit mode the input to the Tx filter will be connected to a mid level. In receive mode the modem will continue to measure the received data quality and extract bits from the received signal, supplying them to the de-interleave buffer, but will otherwise ignore the received data.

#### Command Register B7: Acquire Bit Clock

This bit has no effect in transmit mode.

In receive mode, whenever a byte with the Acquire Bit Clock set to '1' is written to the Command Register, and TASK is not set to RESET, it initiates an automatic sequence designed to achieve bit timing synchronisation with the received signal as quickly as possible. This involves setting the Phase Locked Loop of the received bit timing extraction circuits to its widest bandwidth, then gradually reducing the bandwidth as timing synchronisation is achieved, until it reaches the 'normal' value set by the PLL Control bits of the Control Register.

Setting this bit to '0' (or changing it from '1' to '0') has no effect, however note that the acquisition sequence will be re-started every time that a byte written to the Command Register has the Acquire Bit Clock bit set to '1'. Details of the acquisition sequence are in section 5.1.4.3.

The Acquire Bit Clock will normally be set to '1' up to 12 bits before an SFS (Search for Frame Sync) or SFH (Search for Frame Head) task, however it may also be used independently to reestablish clock synchronisation quickly after a long fade. Alternatively, a SFS or SFH task may be written to the Command Register with the Acquire Bit Clock bit set to '0' if it is known that clock synchronisation does not need to be re-established. Details of the acquisition sequence are in section 5.1.4.3.

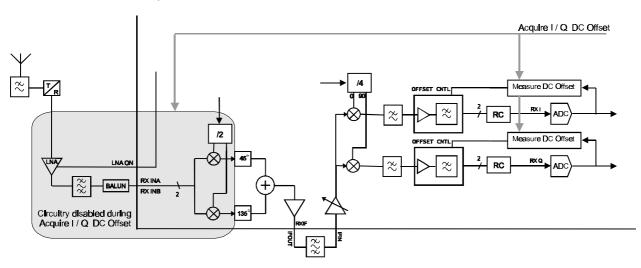

#### Command Register B6: Acquire I Q Offset

This bit has no effect in transmit mode.

In receive mode, when this bit is changed from a '0' to a '1' it initiates an automatic sequence designed to compensate the gross dc offset of the received I and Q signal. This sequence involves temporarily disabling the RF input and setting the analogue offset measurement circuits to compensate for the resulting I and Q dc offset. Once this has been completed the RF input will be reasserted and remaining I and Q offsets will be measured and compensated depending on the setting of bits 4 and 5 of the Control Register (\$02).

Changing this bit from '1' to '0' will terminate acquisition and the 'normal' value set by bits 4 and 5 of the Control Register (\$02) will be carried out.

The Acquire I Q Offset bit will normally be set after changing or reacquiring a channel (e.g. after powering up from a sleep condition). This would normally be done so the acquisition sequence was completed before an SFS or SFH task is initiated. Alternatively, a SFS or SFH task may be written to the Command Register without previously setting the Acquire I Q Offset bit to '1' if it is known that there is no need to re-establish the received signal offsets, e.g. when receiving another message on the same channel in quick succession. Details of the acquisition sequence are in section 5.1.4.3.

The error rate is highest immediately after an Acquire Bit Clock and Acquire I Q Offset sequence is triggered and rapidly reduces to its static value soon after. These erroneous bits could incorrectly trigger the frame sync detection circuits and so it is suggested that a SFH or SFS task is set 12 bits after setting the Acquire Bit Clock sequence and when the Acquire I Q Offset has completed.

## **Command Register B5: Acquire AFC**

This bit has no effect in transmit mode.

In receive mode, when this bit is changed from a '0' to a '1' it initiates an automatic sequence designed to measure and compensate for small differences in the carrier frequencies of the transmitter and receiver. If the TCXO frequency is too far out the dc offset in the demodulated signal will become excessive and limit the decode performance of the device. In these cases the host must adjust the TCXO frequency via the on chip DAC based on the value read from the Frequency Offset register (\$04).

In Mobitex systems the carrier frequencies of basestations are very accurate compared to the permitted tolerances of mobile units. Therefore once a mobile unit has set up it's local TCXO frequency it should be suitable for transmitting or receiving with any basestation. The Slow tracking mode should be sufficient to track any variations caused by environmental changes. Details of the acquisition sequence are in section 5.1.4.3.

#### Command Register B4: Enable packet detect

This bit has no effect in transmit mode.

In receive mode if this bit is set to '1' the device will monitor the demodulated waveform for signals likely to be valid data. The likely presence of valid data will be reported via bit 0 of Status Register 1. This information can assist in the timing of setting a SFS or SFH task. Note

that some noise signals may appear in the baseband as valid data, the RSSI signal should be used to confirm that the received signal is suitable before relying on this signal.

It is recommended that this bit is only set to '1' when searching for the start of a packet. Once a frame sync has been detected this bit should be set to '0' until the start of a new packet needs to be found.

#### Command Register B3, B2, B1, B0: Task

Operations such as transmitting a data block are treated by the modem as 'tasks' and are initiated when the  $\mu C$  writes a byte to the Command Register with the TASK bits set to one of the data handling commands (marked BOLD in the table below).

Mobitex modem tasks:

| В3 | B2 | B1 | B0 |       | Receive Mode Transmit Mode |       |                            |

|----|----|----|----|-------|----------------------------|-------|----------------------------|

| 0  | 0  | 0  | 0  | NULL  |                            | NULL  |                            |

| 0  | 0  | 0  | 1  | SFH   | Search for Frame Head      | T7H   | Transmit 7 byte Frame Head |

| 0  | 0  | 1  | 0  | R3H   | Read 3 byte Frame Head     |       | Reserved                   |

| 0  | 0  | 1  | 1  | RDB   | Read Data Block            | TDB   | Transmit Data Block        |

| 0  | 1  | 0  | 0  | SFS   | Search for Frame Sync      | TQB   | Transmit 4 Bytes           |

| 0  | 1  | 0  | 1  | RSB   | Read Single Byte           | TSB   | Transmit Single Byte       |

| 0  | 1  | 1  | 0  | LFSB  | Load Frame Sync Bytes      | TSO   | Transmit Scrambler Output  |

| 0  | 1  | 1  | 1  | RESET | Cancel any current action  | RESET | Cancel any current action  |

| 1  | 0  | 0  | 1  | SFHZ  | SFH with zero errors       |       | Reserved                   |

| 1  | 0  | 1  | 1  | RSD   | Read Short Data Block      | TSD   | Transmit Short Data Block  |

| 1  | 1  | 0  | 0  | SFSZ  | SFS with zero errors       |       | Reserved                   |

Note: All other bit patterns are reserved.

Bold text indicates a 'data handling command'

The µC should not write a data handling command to the Command Register or write to or read from the Data Buffer when the BFREE (Buffer Free) bit of the Status 1 Register is '0'.

Different tasks apply in receive and transmit modes. Detailed timings for the various tasks are given in Figures 14 and 15.

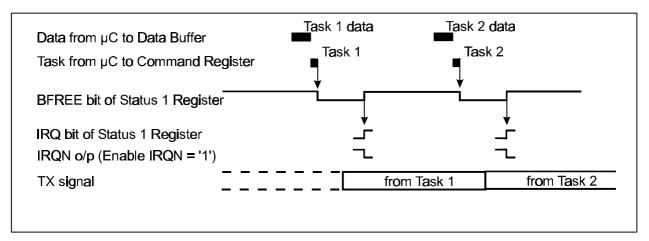

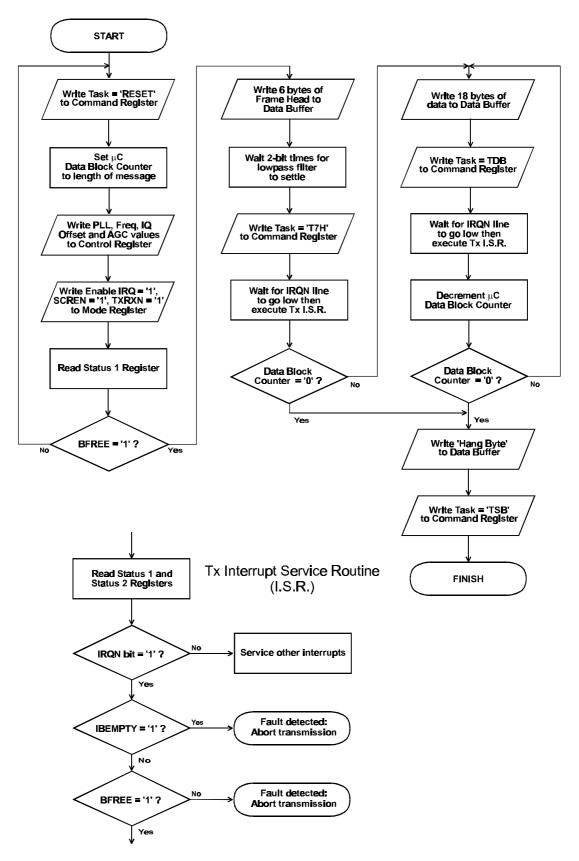

#### **Transmit Operation**

When the modem is in transmit mode, all data handling commands other than TSO instruct the modem to transmit data from the Data Buffer, formatting it as required. For these tasks the  $\mu C$  should wait until the BFREE (Buffer Free) bit of the Status 1 Register is '1', before writing the data to the Data Buffer. If more than 1 byte needs to be written to the Data Buffer, byte number 0 of the block should be written first. The host should then write the desired task to the Command Register.

Once the byte containing the desired task has been written to the Command Register, the modem will:

Set the BFREE (Buffer Free) bit of the Status 1 Register to '0'.

Take the data from the Data Buffer as quickly as it can - transferring it to the Interleave Buffer for eventual transmission. This operation will start immediately if the modem is 'idle' (i.e. not transmitting data from a previous task), otherwise it will be delayed until there is sufficient room in the Interleave Buffer.

Once all of the data has been transferred from the Data Buffer the modem will set the BFREE and IRQ bits of the Status 1 Register to '1', (causing the chip IRQN output to go low if the IRQ Enable bit of the Mode Register has been set to '1') to tell the  $\mu$ C that it may write new data and the next task to the modem.

In this way the  $\mu C$  can write a task and the associated data to the modem while the modem is still transmitting the data from the previous task. See Figure 12.

Figure 12 The Transmit Process

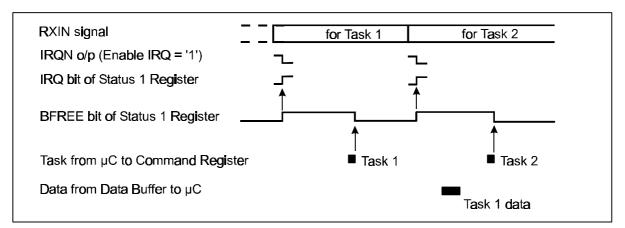

#### **Receive Operation**

When the modem is in receive mode, the  $\mu$ C should wait until the BFREE bit of the Status 1 Register is '1', then write the desired task to the Command Register.

Once the byte containing the desired task has been written to the Command Register, the modem will:

Set the BFREE bit of the Status Register to '0'.

Wait until enough received bits are in the De-interleave Buffer.

Decode them as needed, and transfer any resulting data to the Data Buffer.

Then the modem will set the BFREE and IRQ bits of Status 1 Register to '1', (causing the IRQN output to go low if the IRQ Enable bit of the Mode Register has been set to '1') to tell the  $\mu$ C that it may read from the Data Buffer and write the next task to the modem. If more than 1 byte is contained in the Data Buffer, byte number '0' of the data will be read first.

In this way the  $\mu$ C can read data and write a new task to the modem while the received bits needed for this new task are being stored in the De-interleave Buffer. See Figure 13.

The above is not true for loading the Frame Sync detection bytes (LFSB): the bytes to be compared with the incoming data must be loaded prior to the task bits being written.

Figure 13 The Receive Process

#### **Task Descriptions:**

#### **NULL - No effect**

This task is provided so the acquisition commands can be issued without loading a new task.

#### SFH - Search for Frame Head

Causes the modem to search the received signal for a Frame Head. The Frame Head will consist of a 16-bit Frame Sync followed by control data (see Figure 11 - Mobitex Over Air Signal). The search will continue until a Frame Head has been found, or until the RESET task is loaded.

The search is carried out by first attempting to match the incoming bits against the previously programmed (task LFSB) 16-bit Frame Sync pattern (allowing up to any one bit (of 16) in error). When a match has been found, the modem will read the next 3 received bytes as Frame Head bytes, these bytes will be checked, and corrected if necessary, using the FEC bits. The two Frame Head Data bytes are then placed into the Data Buffer.

The BFREE and IRQ bits of the Status 1 Register will then be set to a logic '1' to indicate that the  $\mu$ C may read the 2 Frame Head Data bytes from the Data Buffer and write the next task to the Command Register. If the FEC indicates uncorrectable errors the modem will set the CRCFEC bit in the Status 1 Register to a logic '1'. The MOBAN bit (Mobile or Base) in the Status 1 Register will be set according to the polarity of the 3 bits preceding the Frame Sync pattern.

#### R3H - Read 3-byte Frame Head

This task, which would normally follow an SFS task, will place the next 3 bytes directly into the Data Buffer. It also causes the modem to check the 3 bytes as Frame Head control data bytes and will set the CRCFEC bit to a logic '1' (high) only if the FEC bits indicate uncorrectable errors. Note: This task will not correct any errors and, due to the Mobitex FEC specification, will not detect all possible uncorrectable error patterns. The BFREE and IRQ bits of the Status 1 Register will be set to '1' when the task is complete to indicate that the  $\mu$ C may read the data from the Data Buffer and write the next task to the modem's Command Register.

The CRCFEC bit in the Status 1 Register will be set according to the validity of the received FEC bits.

## **RDB - Read Data Block**

This task causes the modem to read the next 240 bits as a Mobitex Data Block.

It will de-scramble and de-interleave the bits, FEC correct and CRC check the resulting 18 data bytes and place them into the Data Buffer, setting the BFREE and IRQ bits of the Status 1 Register to '1' when the task is complete to indicate that the  $\mu$ C may read the data from the Data Buffer and write the next task to the modem's Command Register. The CRCFEC bit will be set according to the outcome of the CRC check.

Note: in receive mode the CRC checksum circuits are initialised on completion of any task other than NULL.

#### SFS - Search for Frame Sync

This task, which is intended for special test and channel monitoring purposes, performs the first part only of a SFH task. It causes the modem to search the received signal for a 16-bit sequence which matches the Frame Synchronisation pattern with up to any 1 bit in error.

When a match is found the modem will set the BFREE and IRQ bits of the Status 1 Register to '1' and update the MOBAN bit. The  $\mu$ C may then write the next task to the Command Register.

#### **RSB - Read Single Byte**

This task causes the modem to read the next 8 bits and translate them directly (without deinterleaving or FEC) to a single byte which is placed into the Data Buffer (B7 will represent the earliest bit received). The BFREE and IRQ bits of the Status 1 Register will then be set to '1' to indicate that the  $\mu$ C may read the data byte from the Data Buffer and write the next task to the Command Register.

This task is intended for special tests and channel monitoring - perhaps preceded by an SFS task.

#### LFSB - Load Frame Sync Bytes

This task takes 2 bytes from the Data Buffer and updates the Frame Sync detect bytes. The MSB of byte '0' is compared to the first bit of a received Frame Sync pattern and the LSB of byte '1' is compared to the last bit of a received Frame Sync pattern. This task does not enable Frame Sync detection.

Unlike other Rx tasks, the data buffer must be loaded before the task is issued and the task must only be issued 'between' received messages, i.e. before the first task for receiving a message and after the last data is read out of the data buffer.

Once the modem has read the Frame Sync bytes from the Data Buffer, the BFREE and IRQ bits of the Status 1 Register will be set to '1', indicating to the  $\mu$ C that it may write the next task to the modem.

#### SFHZ - Search for Frame Head with Zero Errors

This performs the same task as SFH task but allowing no bits to be in error over the 16-bit Frame Sync pattern.

#### **RSD - Read Short Data Block**

This task causes the modem to read the next 72 bits as a Mobitex Short Data Block.

It will de-scramble and de-interleave the bits, FEC correct and CRC check the resulting 4 data bytes and place them into the Data Buffer, setting the BFREE and IRQ bits of the Status 1 Register to '1' when the task is complete to indicate that the  $\mu$ C may read the data from the Data Buffer and write the next task to the modem's Command Register. The CRCFEC bit will be set according to the outcome of the CRC check.

Note: in receive mode the CRC checksum circuits are initialised on completion of any task other than NULL.

#### SFSZ - Search for Frame Sync with Zero Errors

This performs the same task as SFS task but allowing no bits to be in error over the 16-bit Frame Sync pattern.

#### T7H - Transmit 7-byte Frame Head

This task takes 6 bytes of data from the Data Buffer, calculates and appends 8 bits of FEC from bytes '4' and '5' then transmits the result as a complete Mobitex Frame Head.

Bytes '0' and '1' form the bit sync pattern, bytes '2' and '3' form the frame sync pattern and bytes '4' and '5' are the frame head control bytes. Bit 7 of byte '0' of the Data Buffer is sent first, bit 0 of the FEC byte last.

Once the modem has read the data bytes from the Data Buffer, the BFREE and IRQ bits of the Status 1 Register will be set to '1', indicating to the  $\mu$ C that it may write the next task and its data to the modem.

#### **TQB - Transmit 4 Bytes**

This task takes 4 bytes of data from the Data Buffer and transmits them, bit 7 first.

Once the modem has read the data bytes from the Data Buffer, the BFREE and IRQ bits of the Status 1 Register will be set to '1', indicating to the  $\mu$ C that it may write the next task and its data to the modem.

#### **TDB - Transmit Data Block**

This task takes 18 bytes of data from the Data Buffer, calculates and applies a 16-bit CRC and forms the FEC for the 18 data bytes and the CRC. This data is then interleaved and passed through the scrambler, if enabled, before being transmitted as a Mobitex Data Block.

Once the modem has read the data bytes from the Data Buffer, the BFREE and IRQ bits of the Status Register will be set to '1', indicating to the  $\mu$ C that it may write the next task and its data to the modem.

Note: In transmit mode the CRC checksum circuit is initialised on completion of any task other than NULL.

#### **TSB - Transmit Single Byte**

This task takes a byte from the Data Buffer and transmits the 8 bits, bit 7 first.

Once the modem has read the data byte from the Data Buffer, the BFREE and IRQ bits of the Status 1 Register will be set to '1', indicating to the  $\mu$ C that it may write the next task and its data to the modem.

#### **TSO - Transmit Scrambler Output**

This task, intended for channel set-up, enables the scrambler and transmits its output.

When the modem has started the task the Status 1 Register bits will not change and hence these will not raise an IRQ. The  $\mu$ C may write the next task and its data to the modem at any time and the scrambler output will stop when the new task has produced its first data.

#### **TSD - Transmit Short Data Block**

This task takes 4 bytes of data from the Data Buffer, calculates and applies a 16-bit CRC and forms the FEC for the 4 data bytes and the CRC. This data is then interleaved and passed through the scrambler, if enabled, before being transmitted as a Mobitex Data Block.

Once the modem has read the data bytes from the Data Buffer, the BFREE and IRQ bits of the Status 1 Register will be set to '1', indicating to the  $\mu C$  that it may write the next task and its data to the modem.

Note: In transmit mode the CRC checksum circuit is initialised on completion of any task other than NULL.

#### **RESET - Stop any current action**

This task takes effect immediately, and terminates any current task the modem may be performing and sets the BFREE bit of the Status 1 Register to '1', without setting the IRQ bit. It should be used when V<sub>DD</sub> is applied to set the modem into a known state.

Note that due to delays in the internal circuitry, it will take approximately 3 bit times for any change to become apparent at the transmitter output.

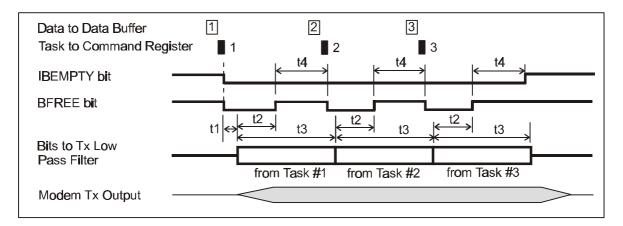

# **Task Timings**

The device should not write to the Command Register whenever the Enable Baseband bit is changed from '0' to '1' and for at least 2 bit times after the following:

Changing the Tx/Rx bit.

Resetting or after power is applied to the device.

This is to ensure that the internal operation of the device is initialised correctly for the new task. Note that this only applies to the Command Register, the other registers may be accessed as normal.

Figure 14 Transmit Mode Timing Diagram

|    |                                                                                                                 | Task | Typical time<br>(bit-times) |

|----|-----------------------------------------------------------------------------------------------------------------|------|-----------------------------|

| t1 | Time from writing first task (modem in 'idle' state) to application of first transmit bit to Tx Low Pass filter | Any  | 1                           |

| t2 | Time from application of first bit of                                                                           | T7H  | 36                          |

|    | task to Tx Low Pass filter until BFREE                                                                          | TQB  | 24                          |

|    | goes to a logic '1' (high)                                                                                      | TDB  | 20                          |

|    |                                                                                                                 | TSB  | 1                           |

|    |                                                                                                                 | TSD  | 6                           |

| t3 | Time to transmit all bits of task                                                                               | T7H  | 56                          |

|    |                                                                                                                 | TQB  | 32                          |

|    |                                                                                                                 | TDB  | 240                         |

|    |                                                                                                                 | TSB  | 8                           |

|    |                                                                                                                 | TSD  | 72                          |

| t4 | Max time allowed from BFREE going to a                                                                          | T7H  | 18                          |

|    | logic '1' (high) for next task (and data) to                                                                    | TQB  | 6                           |

|    | be written to modem                                                                                             | TDB  | 218                         |

|    |                                                                                                                 | TSB  | 6                           |

|    |                                                                                                                 | TSD  | 64                          |

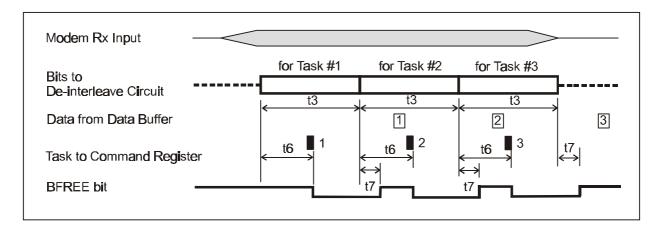

Figure 15 Receive Mode Timing Diagram

|    |                                                                                                | Task | Typical time (bit-times) |

|----|------------------------------------------------------------------------------------------------|------|--------------------------|

| t3 | Time to receive all bits of task                                                               | SFH  | 56                       |

|    |                                                                                                | R3H  | 24                       |

|    |                                                                                                | RDB  | 240                      |

|    |                                                                                                | RSB  | 8                        |

|    |                                                                                                | RSD  | 72                       |

| t6 | Maximum time between first bit of task                                                         | SFH  | 14                       |

|    | entering de-interleave circuit and task                                                        | R3H  | 18                       |

|    | being written to modem                                                                         | RDB  | 218                      |

|    |                                                                                                | RSB  | 6                        |

|    |                                                                                                | RSD  | 64                       |

| t7 | Time from last bit of task entering de-interleave circuit to BFREE going to a logic '1' (high) | Any  | 1                        |

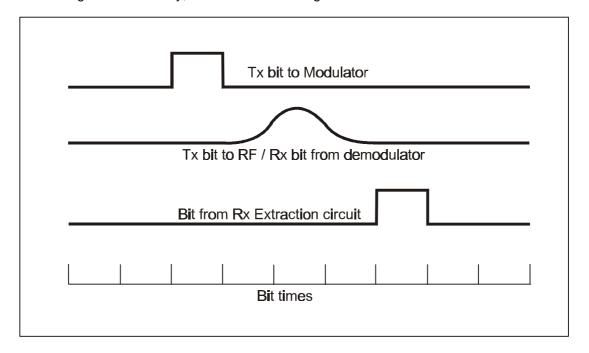

#### Tx and Rx Low Pass Filter Delay

The previous task timing figures are based on the signal at the input to the RF sections (in transmit mode) or the input to the de-interleave buffer (in receive mode). There is an additional delay of about 2 bit times in both transmit and receive modes due to the Tx/Rx filtering and RF circuitry, as illustrated in the figure below.

Figure 16 Low Pass Filter Delay

#### 5.1.4.3 Control Register

This 8-bit write only register controls the response times of the receive clock extraction and signal level measurement circuits.

| Contro | ol Register | \$02 | Write             |   |                                  |   |             |   |  |

|--------|-------------|------|-------------------|---|----------------------------------|---|-------------|---|--|

| Bit:   | 7           | 6    | 5                 | 4 | 3                                | 2 | 1           | 0 |  |

|        | AGC Control |      | IQ Offset Control |   | Frequency tracking (AFC) Control |   | PLL Control |   |  |

The modem needs to make accurate measurements of the received signal level, dc offset and frequency offset and bit timing to achieve reasonable error rates. Accurate measurements, especially in the presence of noise, are best made by averaging over a relatively long time.

However, in most cases the modem will be used to receive isolated messages from a distant transmitter and may be turned on for a very short time before the message starts. Also, the received baseband signal out of the radio's frequency discriminator will have a dc offset due to small differences between the receiver and transmitter reference oscillators and hence their 'carrier' frequencies.

To cater for this situation acquire bits 7 to 5 are provided in the Command register (\$01) which, when triggered, cause the modem to follow an automatic sequence designed to perform these measurements as quickly as possible. After these acquisition sequences have completed the circuits return to the mode as set in this register.

# Control Register B7, B6: AGC Control

These two bits have no effect in transmit mode.

In receive mode these bits set the response of the AGC circuit. The 'Run' and 'Max Gain and Run' settings allow the circuit to acquire and track incoming signals.

| B7 | B6 | Setting Action    |                                                 |  |  |  |  |

|----|----|-------------------|-------------------------------------------------|--|--|--|--|

| 0  | 0  | Max Gain and Hold | AGC set to maximum gain and held                |  |  |  |  |

| 0  | 1  | Hold*             | AGC gain not updated by internal circuit        |  |  |  |  |

| 1  | 0  | Run               | AGC tracks input signal                         |  |  |  |  |

| 1  | 1  | Max Gain and Run  | AGC set to maximum gain and tracks input signal |  |  |  |  |

<sup>\*</sup> Host may override AGC setting by writing to \$19 only when this setting is selected.

#### Control Register B5, B4: I/Q Offset Control

These two bits have no effect in transmit mode.

In receive mode, these set the 'normal' response of the I/Q offset measuring circuits. The offset control is in two sections, an analogue 'coarse' setting and a digital 'fine' setting. The host may read and directly overwrite the coarse setting via registers \$18 and \$19. The coarse and fine settings will be overridden by the Acquire I Q Offset command (bit 6 of Command register) which will go through a sequence of:

#### Reset

Run with Coarse Tracking for 12 bits to correct gross I/Q offset error Run with Fine Tracking for 640 bits to adjust for remaining I/Q offsets Revert to normal setting (hold / fine / coarse)

| B5 | B4 | Setting Action  |                                             |  |  |  |  |

|----|----|-----------------|---------------------------------------------|--|--|--|--|

| 0  | 0  | Reset and Hold  | I/Q offset tracking reset and held          |  |  |  |  |

| 0  | 1  | Hold*           | I/Q offset tracking held at current setting |  |  |  |  |

| 1  | 0  | Fine Tracking*  | I/Q fine offset tracking                    |  |  |  |  |

| 1  | 1  | Coarse Tracking | I/Q coarse offset tracking                  |  |  |  |  |

<sup>\*</sup>Host may override Coarse I/Q Offset by writing to registers \$18 and \$19 only when these settings are selected and bit 6 of Command register is = '0'.

# Control Register B3, B2: Frequency tracking (AFC) Control

These two bits have no effect in transmit mode.

In receive mode, they set the 'normal' response of the frequency tracking circuits. This setting will be temporarily overridden by the Acquire AFC command (bit 5 of Command register) which will go through a sequence of:

#### Reset

Run with Fast Tracking for 96 bits to correct frequency offset error Run with Slow Tracking for 750 bits to follow any further frequency offsets Revert to normal setting (hold / slow / fast)

| B3 | B2 | Setting Action |                                            |  |  |  |  |

|----|----|----------------|--------------------------------------------|--|--|--|--|

| 0  | 0  | Reset and Hold | Frequency tracking reset and held          |  |  |  |  |

| 0  | 1  | Hold           | Frequency tracking held at current setting |  |  |  |  |

| 1  | 0  | Slow Tracking  | Frequency slow tracking                    |  |  |  |  |

| 1  | 1  | Fast Tracking  | Frequency fast tracking                    |  |  |  |  |

For Mobitex systems, and most general purpose applications using the modem, these bits should normally be set to Slow Tracking after the host has activated the automatic sequence.

The Fast setting allows the modem to respond quickly without µC intervention - although at the cost of reduced Bit Error Rate versus Signal to Noise performance.

Note that the AFC measuring system requires '00' and '11' bit pairs to be received at reasonably frequent intervals. The AFC tracking will eventually fail if '1' or '0' is transmitted continuously.

# Control Register B1, B0: PLL Control

These two bits have no effect in transmit mode.

In receive mode, they set the 'normal' bandwidth of the Rx clock extraction Phase Locked Loop circuit. This setting will be temporarily overridden by the Acquire Bit Clock command (bit 7 of Command register) which will go through a sequence depending if a frame sync is being searched for (SFH or SFS task is started within 14 bits):

Frame sync search:

Wide setting until Frame Sync is detected

30 bits of medium setting

Revert to normal setting

No frame sync search:

16 bits of wide setting

30 bits of medium setting

Revert to normal setting

| B1 | B0 | PLL Bandwidth | Suggested use                                    |

|----|----|---------------|--------------------------------------------------|

| 0  | 0  | Hold          | Signal fades                                     |

| 0  | 1  | Narrow        | < ± 20ppm bit rate error systems                 |

| 1  | 0  | Medium        | Wide bit rate error or long preamble acquisition |

| 1  | 1  | Wide          | Quick acquisition                                |

The 'hold' setting is intended for use during signal fades, otherwise the minimum bandwidth consistent with the transmit and receive modem bit rate tolerances should be chosen.

The wide and medium bandwidth settings allow the modem to respond rapidly to fresh messages and recover rapidly after a fade without  $\mu C$  intervention - although at the cost of reduced Bit Error Rate versus Signal to Noise performance.

Note that the clock extraction circuits work by detecting the timing of edges, i.e. a change from '0' to '1' or '1' to '0'. The clock extraction will eventually fail if '1' or '0' is transmitted continuously

#### 5.1.4.4 Mode Register

The contents of this 8-bit write only register control the basic operating modes of the modem:

| Mode   | Register      | \$03   | Write |       |                    |                  |                    |                    |

|--------|---------------|--------|-------|-------|--------------------|------------------|--------------------|--------------------|

| Bit: 7 |               | 6      | 5     | 4     | 3                  | 2                | 1                  | 0                  |

|        | IRQ<br>Enable | INVBit | TxRxN | SCREn | En PLL<br>Lock IRQ | Enable DQ<br>IRQ | Enable<br>Main ADC | Enable<br>Main DAC |

#### Mode Register B7: IRQ Enable - IRQN Output Enable

When this bit is set to '1' the IRQN chip output pin is pulled low (to  $V_{SS}$ ) whenever the IRQ bit of the Status Register is a '1'.

#### Mode Register B6: INVBIT - Invert Bits

This bit controls inversion of transmitted and received data. This allows for frequency inversions in the RF chain and has the effect of swapping I and Q paths in both transmitter and receiver.

#### Mode Register B5: TXRXN - Tx/Rx Mode

Setting this bit to '1' puts the modem into Transmit mode, clearing it to '0' puts the modem into Receive mode. When changing from Rx to Tx there must be a 2-bit pause before setting a new task to allow the filter to stabilise. (See also Baseband Enable bit).

Note that changing between receive and transmit modes will cancel any current task. Note also that this bit does not enable Tx or Rx sections of the CMX990 which must be enabled by separate control bits.

#### Mode Register B4: SCREN - Scramble Enable

The scrambler only takes effect during the transmission or reception of a Mobitex Data Block, Short Data Block and during a TSO task. Setting this bit to '1' enables scrambling, clearing it to '0' disables scrambling.

The scrambler is only operative, if enabled by this control bit, during TSO, RDB, RSD, TSD or TDB, it is held in a reset state at all other times.

This bit should not be changed while the modem is decoding or transmitting a Mobitex Data Block.

#### Mode Register B3: En PLL Lock IRQ - Enable Phase Lock Loop lost IRQ

Setting this bit to '1' causes the IRQ bit of the Status 1 Register to be set to '1' whenever The PLL Lock lost bit is set to 1. (The Phase Lock lost bit of Status 2 Register will also be set to '1' at the same time.)

# Mode Register B2: Enable DQ IRQ - Enable Data Quality IRQ

In receive mode, setting this bit to '1' causes the IRQ bit of the Status 1 Register to be set to '1' whenever a new Data Quality reading is ready. (The DQRDY bit of the Status 1 Register will also be set to '1' at the same time.)

In transmit mode this bit has no effect.

# Mode Register B1 - 0: Enable Main ADC / Enable Main DAC

When the respective bit is set to '1' the main ADC and DAC are enabled, power may be saved by setting these bits to '0' when the ADC or DAC are not needed. Bit '0' would normally only be set to '1' when bit 5 is set to '1'. Bit '1' would normally only be set to '1' when bit 5 is set to '0'.

#### 5.1.4.5 Status 1 Register

This register may be read by the µC to determine the current state of the modem.

| Status | 1 Register | \$01  | Read    |        |        |       |       |                  |

|--------|------------|-------|---------|--------|--------|-------|-------|------------------|

| Bit:   | 7          | 6     | 5       | 4      | 3      | 2     | 1     | 0                |

|        | IRQ        | BFREE | IBEMPTY | DIBOVF | CRCFEC | DQRDY | MoBaN | Packet<br>Detect |

#### Status 1 Register, B7: IRQ - Interrupt Request

This bit is set to '1' by:

The Status 1 Register BFREE bit going from '0' to '1', unless this is caused by a RESET task or by a change to the Mode Register Enable Baseband or TXRXN bits

- or The Status 1 Register IBEMPTY bit going from '0' to '1', unless this is caused by a RESET task or by changing the Mode Register Enable Baseband or TXRXN bits

- or The Status 1 Register DQRDY bit going from '0' to '1' (If DQEN = '1').

- or The Status 1 Register DIBOVF bit going from '0' to '1'.

- or The Status 1 Register Packet Detect bit going from '0' to '1' if the Enable Packet Detect bit is set in the Command Register.

- or The Status 2 Register bits 7, 3, 2, 1 or 0 going from '0' to '1'.

The host must read Status 1 Register first after detecting or looking for an interrupt condition. The IRQ bit is cleared to '0' immediately after a read of the Status Register that caused the interrupt. In the case where 1 or more bits in Status 2 Register cause an interrupt the IRQ bit is only cleared after reading Status 2 Register.

If the IRQEN bit of the Mode Register is '1', then the chip IRQN output will be pulled low (to Vss) whenever the IRQ bit is '1'.

#### Status 1 Register, B6: BFREE - Data Buffer Free

This bit reflects the availability of the Data Buffer and is cleared to '0' whenever a task other than NULL, RESET or TSO is written to the Command Register.

In transmit mode, the BFREE bit will be set to '1' (also setting the Status 1 Register IRQ bit to '1') when the modem is ready for the  $\mu C$  to write new data to the Data Buffer and the next task to the Command Register.

In receive mode, the BFREE bit is set to '1' (also setting the Status 1 Register IRQ bit to '1') by the modem when it has completed a task and any data associated with that task has been placed into the Data Buffer. The  $\mu C$  may then read that data and write the next task to the Command Register.

The BFREE bit is also set to '1', but without setting the IRQ bit, by a RESET task or when the Mode Register Enable Baseband or TXRXN bits are changed.

# Status 1 Register, B5: IBEMPTY - Interleave Buffer Empty

In transmit mode, this bit will be set to '1', also setting the IRQ bit, when less than two bits remain in the Interleave Buffer. Any transmit task written to the modem after this bit goes to '1' will be too late to avoid a gap in the transmit output signal.

The bit is also set to '1' by a RESET task or by a change of the Mode Register TXRXN or Enable Baseband bits, but in these cases the IRQ bit will not be set.

The bit is cleared to '0' by writing a task other than NULL, RESET or TSO to the Command Register.

Note: When the modem is in transmit mode and the Interleave Buffer is empty, a mid-level voltage ( $V_{BIAS}$ ) will be applied to the Tx low pass filter.

In receive mode this bit will be '0'.

#### Status 1 Register, B4: DIBOVF - De-Interleave Buffer Overflow

In receive mode this bit will be set to '1' (also setting the IRQ bit) when a task is written to the Command Register too late to allow continuous reception.